# MDE based FPGA physical Design Fast prototyping with Smalltalk

Ciprian Teodorov, Loïc Lagadec

Loic.lagadec@univ-brest.fr

Lab-STICC MOCS UMR 3192

L'Université est une chance

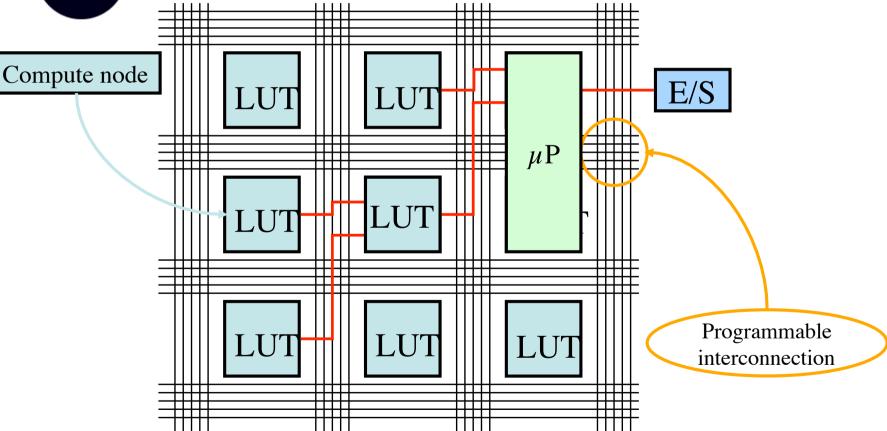

#### **FPGAs**

"Flexible" hardware Time to market Hard to program

Hard to debug

#### **FPGAs**

"Flexible" hardware Time to market Hard to program

Hard to debug

#### **EDA required!**

- •C to circuit

- Debug

- Benchmarking

Our Smalltalk-based EDA legacy

### Legacy backfires

- Early developments (MADEO) started in 1996

- Fast evolving domain (Moore + Murfy)

- Refactoring is not enough to keep in the race

We have to re-design our framework

#### New direction

- We need to shift from

- a generic solution to be tailored on demand

- To

- a repository of model, algorithms, components

- In order to deliver

- Performances

- Scalability

- Flexibility

- Durability

# **LEGACY**

#### Front end

C code

High level synthesis (compilation)

Ressources allocation (logic synthesis)

Circuit

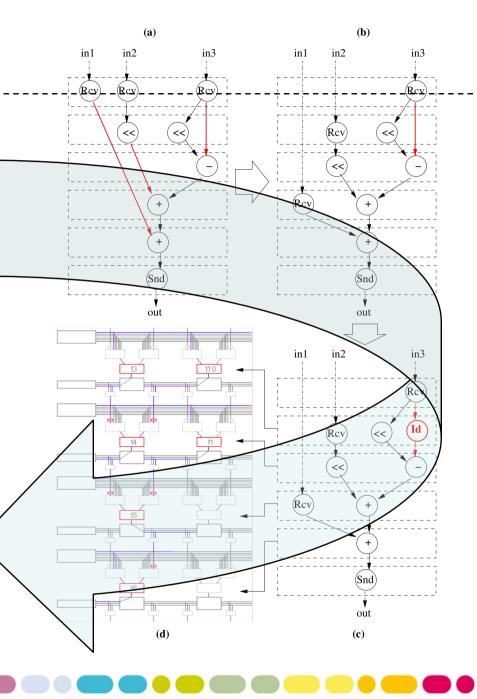

# Programming an FPGA in 4 steps

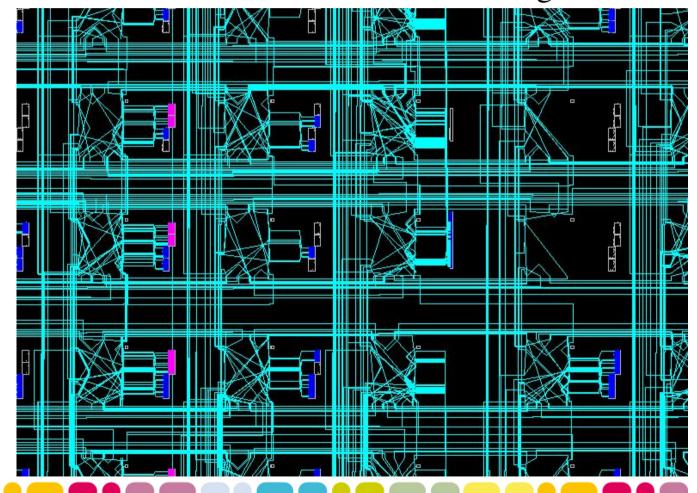

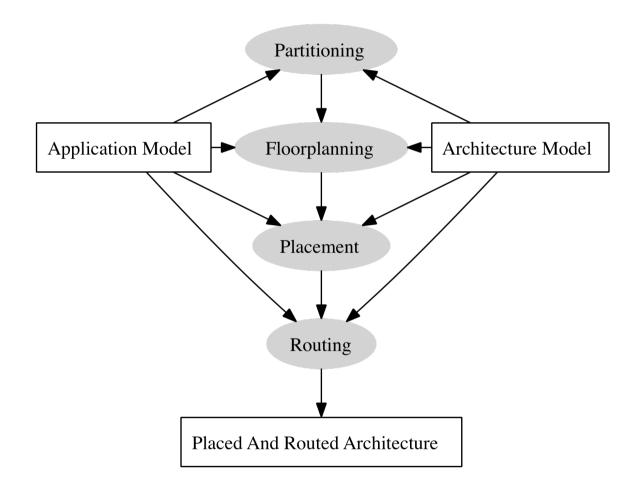

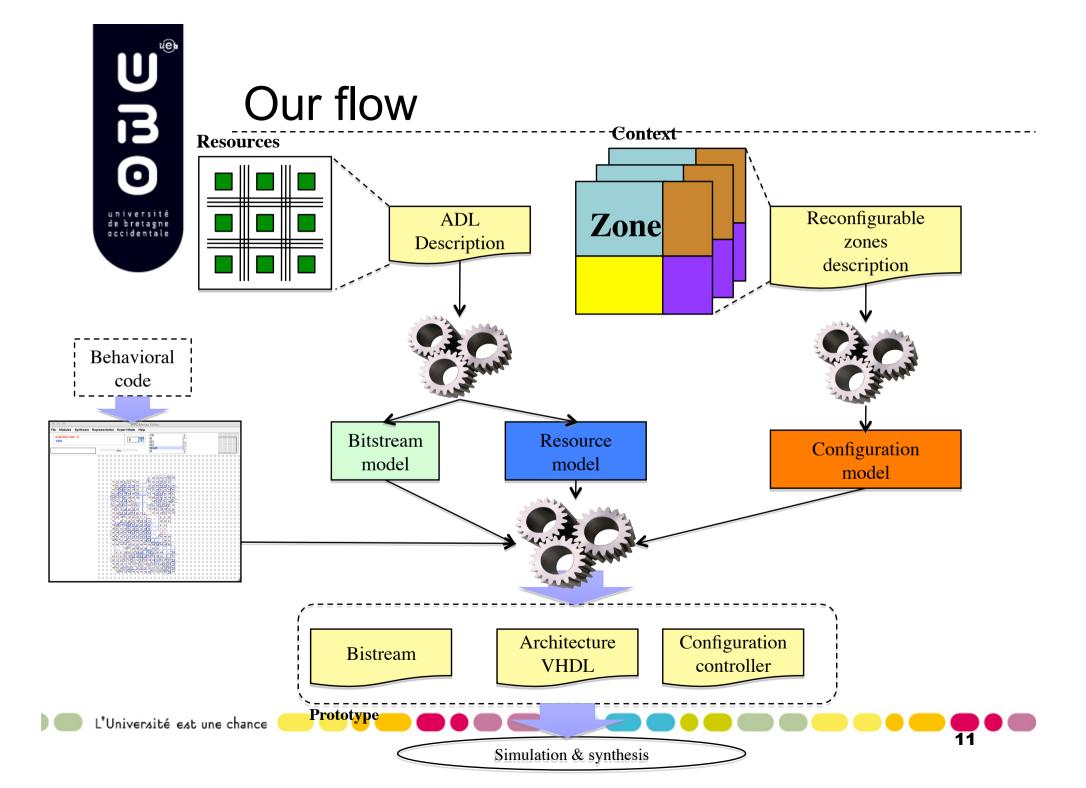

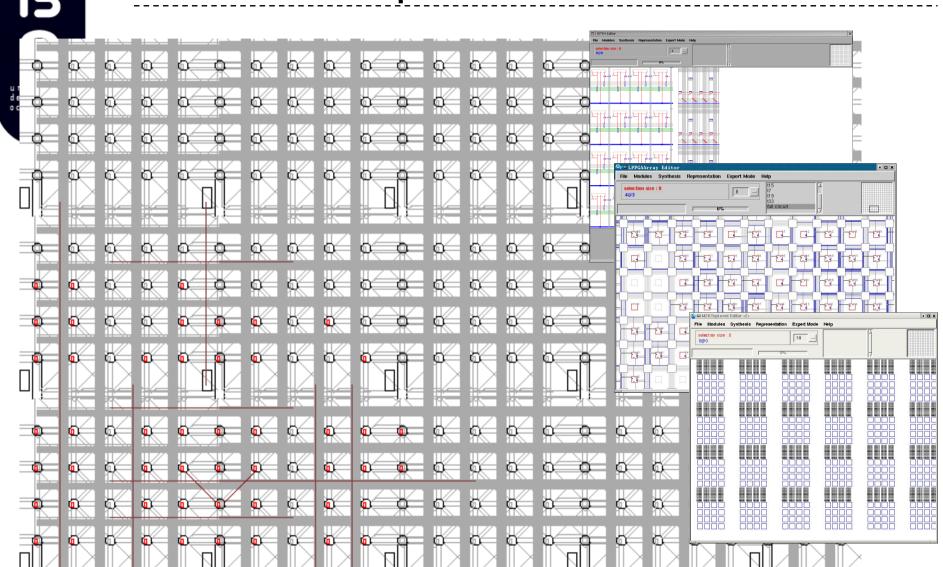

### ADL Based EDA generators

### Some examples

# **RE-DESIGN**

L'Université est une chance

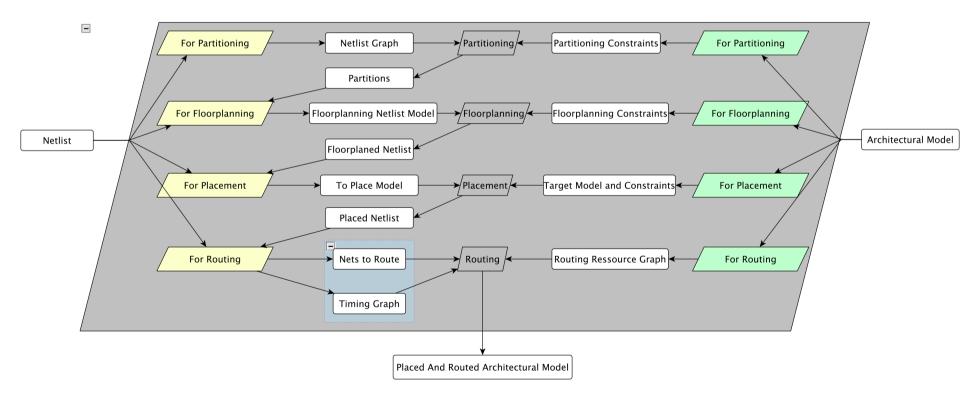

#### Goal oriented view extraction

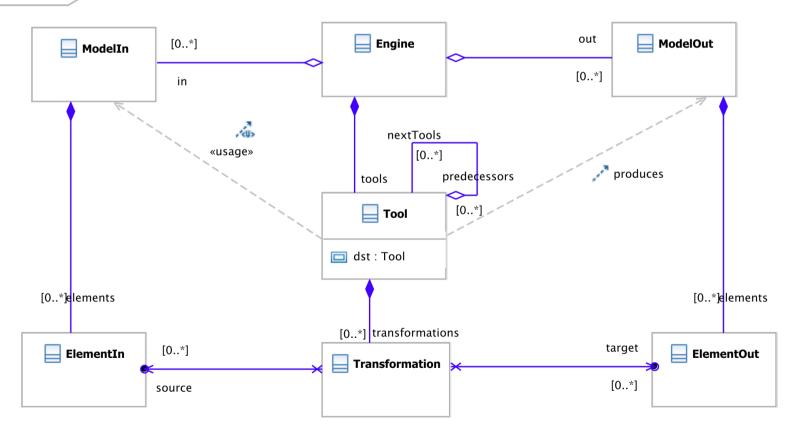

# Tool engine

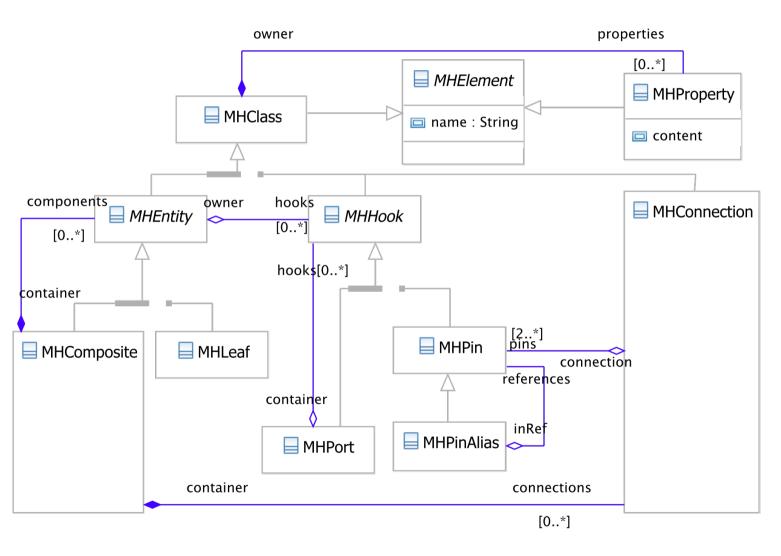

### Models as common vocabulary

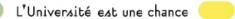

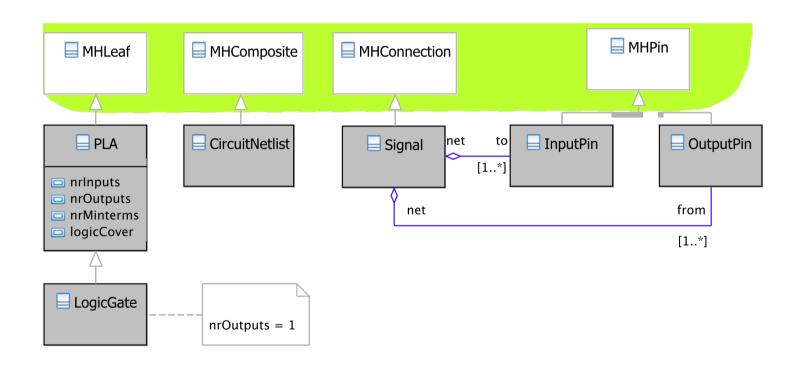

## Combinational circuit modeling

L'Université est une chance

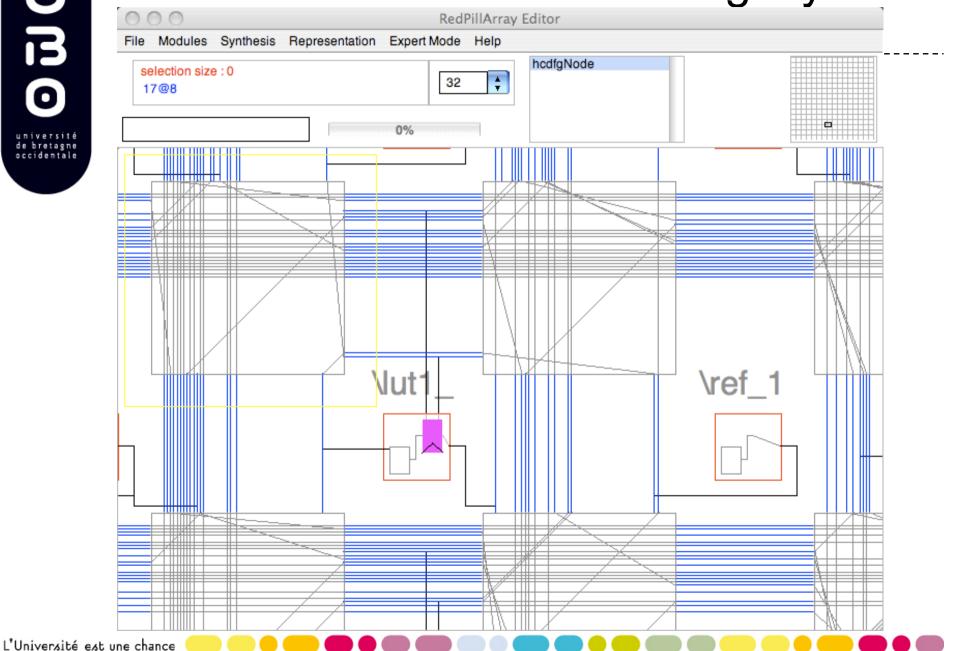

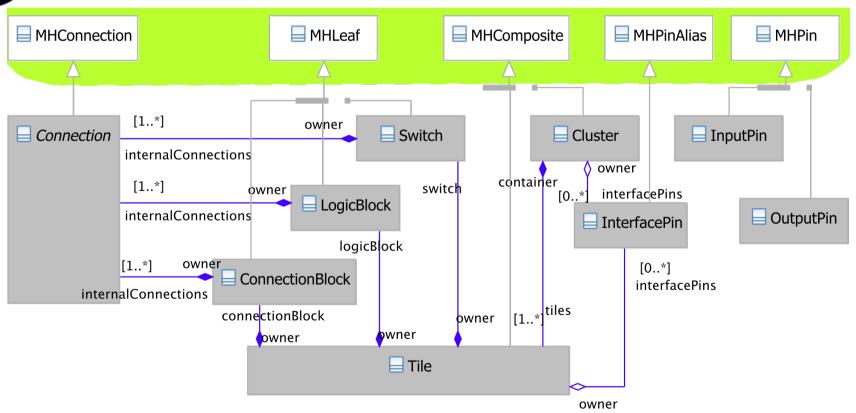

### Target modeling

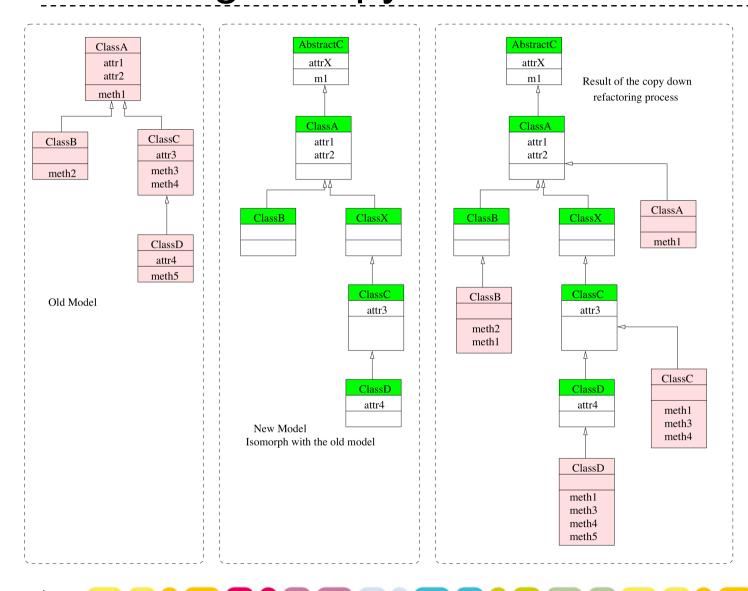

# Re-design / copy down

# CONCLUSION

# Let's try to summarize

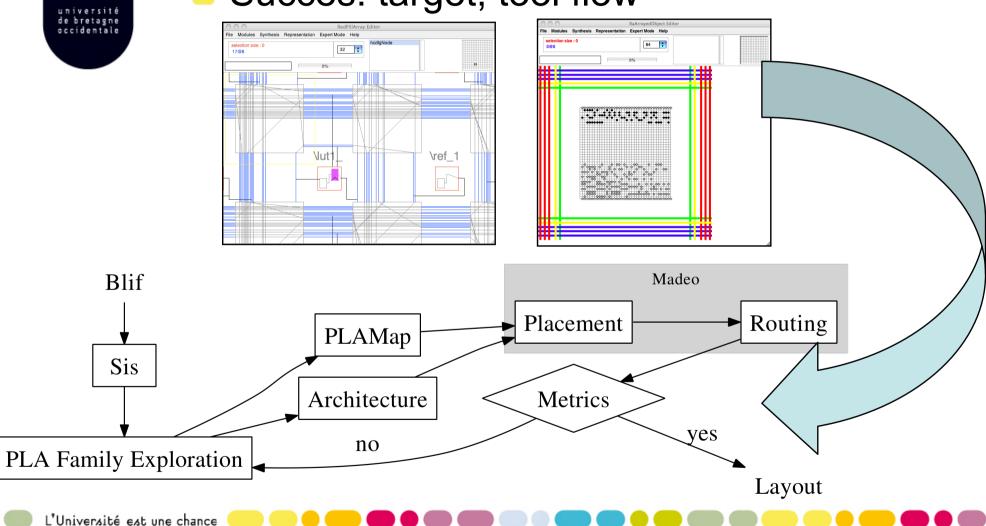

Succes: target, tool flow

#### Conclusion

- Future work:

- Tools integration (eg Mondrian integration)

- Performances improvement

- Test coverage

- Algorithm pick and play GUI

# Thank you for your attention